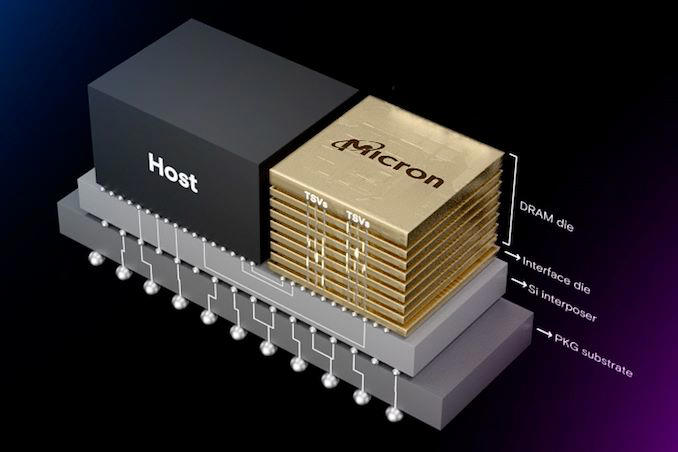

在 HBM4 内存带来的几大变化中,最直接的变化之一就是内存接口的宽度。随着第四代内存标准从已经很宽的 1024 位接口升级到超宽的 2048 位接口,HBM4 内存堆栈将不会像以前一样正常工作;芯片制造商需要采用比现在更先进的封装方法,以适应更宽的内存。

作为 2024 年欧洲技术研讨会演讲的一部分,台积电提供了一些有关其将为 HBM4 制造的基础模具的新细节,这些模具将使用逻辑工艺制造。由于台积电计划采用其 N12 和 N5 工艺的变体来完成这项任务,该公司有望在 HBM4 制造工艺中占据有利地位,因为内存工厂目前还不具备经济地生产这种先进逻辑芯片的能力(如果它们能生产的话)。

对于第一波 HBM4,台积电准备采用两种制造工艺:N12FFC+ 和 N5。虽然它们的目的相同--将 HBM4E 内存与下一代 AI 和 HPC 处理器集成,但它们将以两种不同的方式连接用于 AI 和 HPC 应用的高性能处理器内存。

台积电设计与技术平台高级总监表示:"我们正与主要的 HBM 存储器合作伙伴(美光、三星、SK 海力士)合作,在先进节点上实现 HBM4 全堆栈集成。N12FFC+高性价比基础芯片可以达到HBM的性能,而N5基础芯片可以在HBM4速度下以更低的功耗提供更多的逻辑。"

台积电采用 N12FFC+ 制造工艺(12 纳米 FinFet Compact Plus,正式属于 12 纳米级别的技术,但其根源来自台积电久经考验的 16 纳米 FinFET 生产节点)制造的基础芯片将用于在系统级芯片(SoC)旁边的硅中间件上安装 HBM4 存储器堆栈。台积电认为,他们的 12FFC+ 工艺非常适合实现 HBM4 性能,使内存供应商能够构建 12-Hi(48 GB) 和 16-Hi 堆栈(64 GB),每堆栈带宽超过 2 TB/秒。

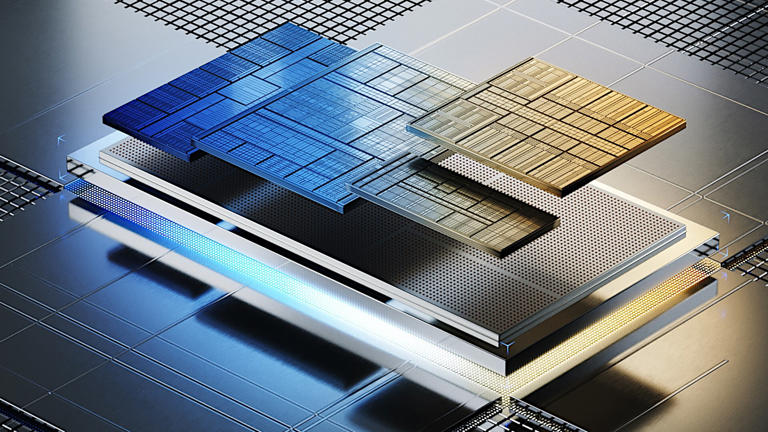

高级总监说:"我们还在为 HBM4 优化 CoWoS-L 和 CoWoS-R。CoWoS-L和CoWoS-R都[使用]超过八层,以实现HBM4的2000多个互连的路由,并具有[适当的]信号完整性"。

N12FFC+ 上的 HBM4 基础芯片将有助于使用台积电的 CoWoS-L 或 CoWoS-R 先进封装技术构建系统级封装 (SiP),该技术可为内插件提供高达 8 倍网纹尺寸的空间,足以容纳多达 12 个 HBM4 存储器堆栈。根据台积电的数据,目前,HBM4 在电流为 14mA 时的数据传输速率可达 6 GT/s。

台积电代表解释说:"我们与 Cadence、Synopsys 和 Ansys 等 EDA 合作伙伴合作,对 HBM4 通道信号完整性、IR/EM 和热精度进行认证。"

同时,作为更先进的替代方案,内存制造商还可以选择台积电的 N5 工艺来生产 HBM4 基础芯片。采用 N5 工艺的基础芯片将包含更多的逻辑,功耗更低,性能更高。但可以说最重要的好处是,这种先进的工艺技术将实现非常小的互连间距,大约为 6 至 9 微米。这将使 N5 基本芯片与直接键合技术结合使用,从而使 HBM4 可以直接在逻辑芯片上进行三维堆叠。直接键合技术可实现更高的内存性能,这对于一直在渴求更多内存带宽的人工智能和高性能计算芯片来说将是一个巨大的推动。

我们已经知道台积电和 SK Hynix 正合作开发 HBM4 基础芯片。台积电很可能也会为美光生产 HBM4 基础芯片。否则,我们会更惊讶地看到台积电与三星合作,因为这家企业集团已经通过其三星代工部门拥有了自己的先进逻辑晶圆厂。

特别声明:以上内容(如有图片或视频亦包括在内)为自媒体平台“早讯网”用户上传并发布,本平台仅提供信息存储服务。

本站所有图片由云图床提供储存服务。

发表评论 取消回复